微机原理吧 关注:3,492贴子:15,882

- 2回复贴,共1页

在现代计算机系统中,处理器通常会有一个快速的缓存(L1 cache)来减少对主内存(RAM)的访问时间。当处理器需要读取或写入数据时,它首先检查最接近的奇数地址是否在缓存中。如果在,那么这个数据就可以在第一个时钟周期中被访问或写入。这被称为“命中”,处理器可以直接从缓存中获取数据,而不需要访问较慢的主内存。

然而,如果需要的数据不在缓存中(即“未命中”),处理器必须从主内存中检索数据,这通常需要两个时钟周期:第一个时钟周期用于发出内存请求,第二个时钟周期用于数据实际到达处理器。在这个过程中,数据被加载到缓存中,以便未来的访问可以更快。

这种情况下,对于奇数地址的访问可能需要两个周期,是因为缓存是以块(通常是连续的内存地址)的方式进行加载的。如果请求的数据不在缓存中,那么可能需要加载一个包含所需数据的缓存块,这个块可能包含了大量的数据,其中就包括紧接着所需数据的下一个奇数地址上的数据。因此,即使我们只需要一个奇数地址上的数据,处理器也可能需要两个时钟周期来加载并访问它。al 回答的希望对你有帮助

然而,如果需要的数据不在缓存中(即“未命中”),处理器必须从主内存中检索数据,这通常需要两个时钟周期:第一个时钟周期用于发出内存请求,第二个时钟周期用于数据实际到达处理器。在这个过程中,数据被加载到缓存中,以便未来的访问可以更快。

这种情况下,对于奇数地址的访问可能需要两个周期,是因为缓存是以块(通常是连续的内存地址)的方式进行加载的。如果请求的数据不在缓存中,那么可能需要加载一个包含所需数据的缓存块,这个块可能包含了大量的数据,其中就包括紧接着所需数据的下一个奇数地址上的数据。因此,即使我们只需要一个奇数地址上的数据,处理器也可能需要两个时钟周期来加载并访问它。al 回答的希望对你有帮助

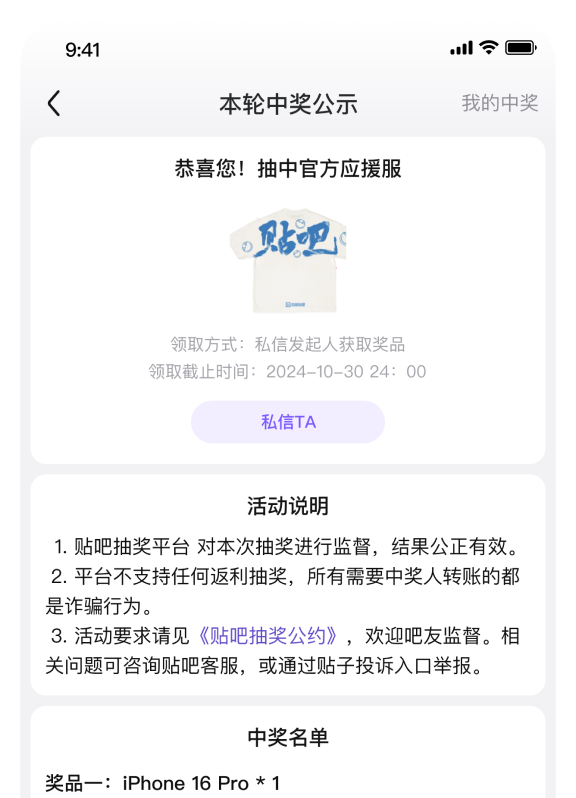

扫二维码下载贴吧客户端

下载贴吧APP

看高清直播、视频!

看高清直播、视频!

贴吧热议榜

- 1货拉拉司机回应与保时捷纠纷2325270

- 2双城之战烂尾的原因找到了2268003

- 3吴柳芳账号被禁止关注1843940

- 4黑神话获英国电影学院奖提名1412181

- 5Scout和Peyz疑似加入JDG1229930

- 6余承东官宣Mate70新功能1062600

- 7涵艺称lng与jdg转会有问题790176

- 8IG新赛季阵容曝光573160

- 9阿莫林曼联首秀平局560032

- 10莱加内斯0比3皇马370920